# 模拟集成电路符号化低阶模型 自动生成方法与应用

## Automatic Generation Method of Low-order Models for Analog Integrated Circuits with Applications

胡翰彬 微纳电子学系 导师:施国勇 教授

Hanbin Hu, Dept. of Micro/Nano-electronics Advisor: Prof. Guoyong Shi

Master Degree Defense, Shanghai Jiao Tong University, January 14, 2016

# Outline

- Research motivation

- Background review

- Main contribution

- Topology simplification algorithm

- Applications (Time-domain & CMRR/PSRR)

- Experimental results

- Conclusion

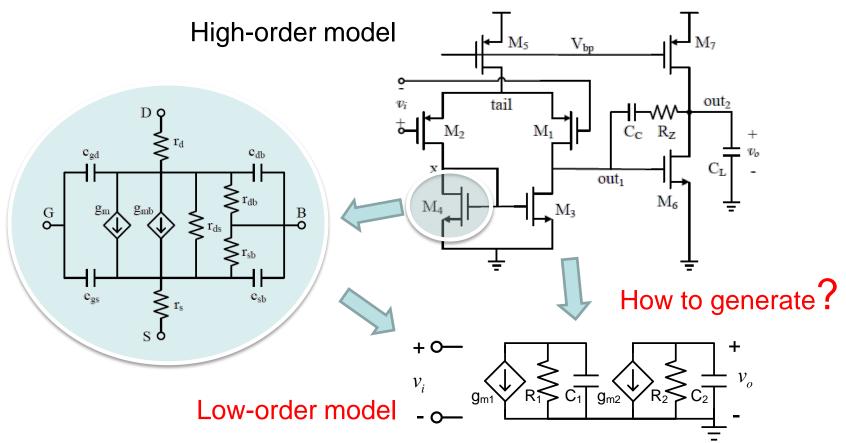

### **Motivation for Model Order Reduction**

#### State of Art in Analog Circuit Design

Hard to capture principal elements in analog circuits

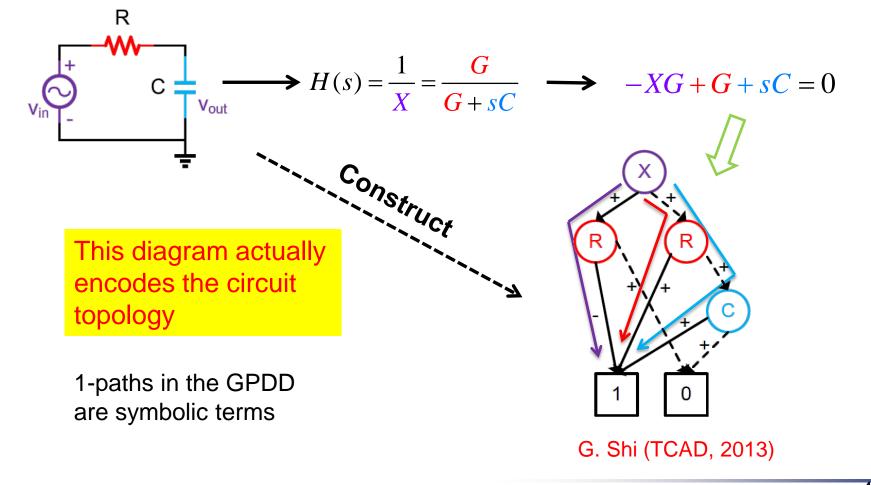

### **Symbolic Analysis**

- Graph-Pair Decision Diagram A BDD-Based Structure

- A topology-based analysis method

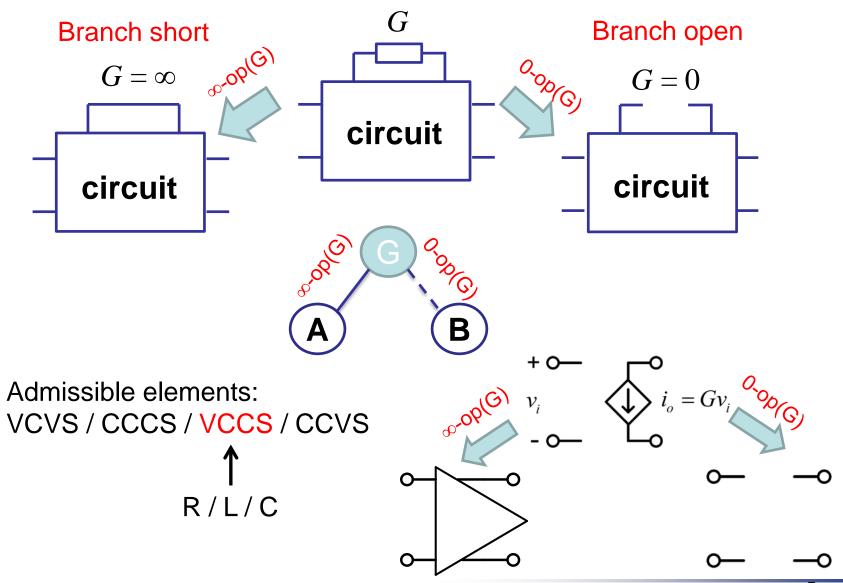

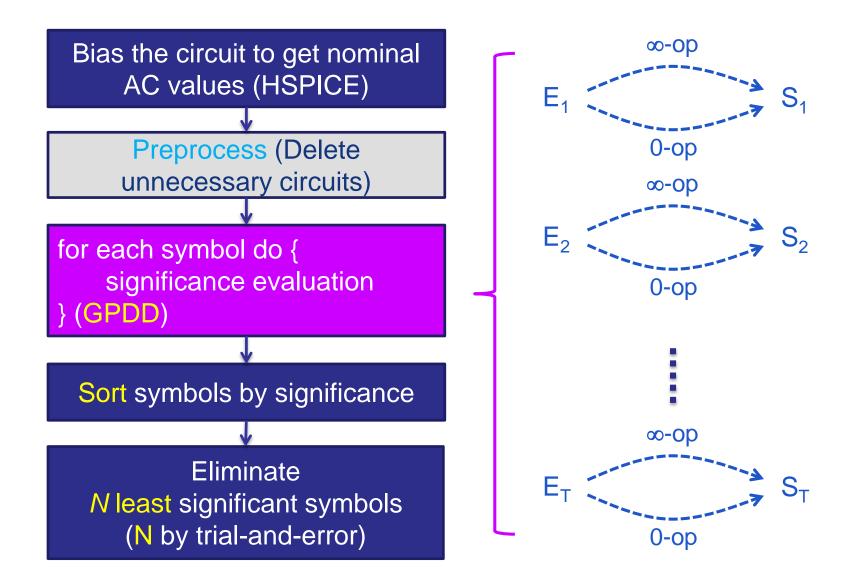

## **Two Operations for Topology Reduction in GPDD**

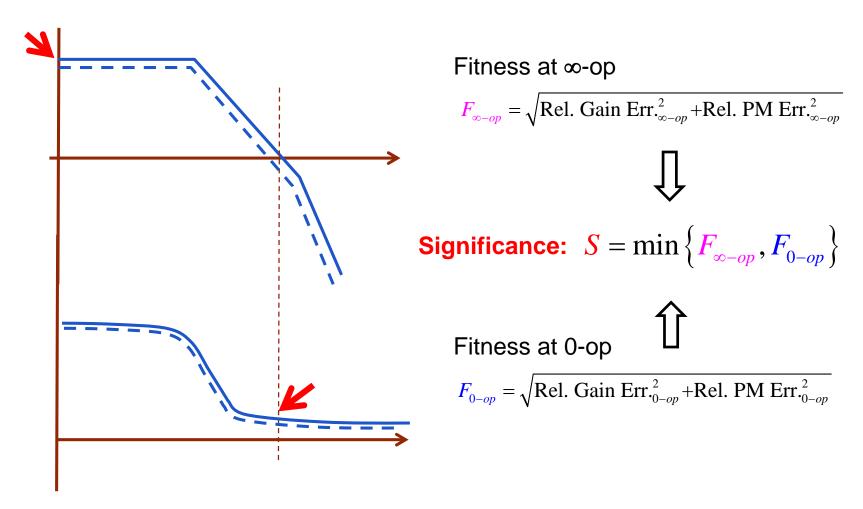

### **Significance Definition**

Significance from two operations

### **Low-order Model Procedure**

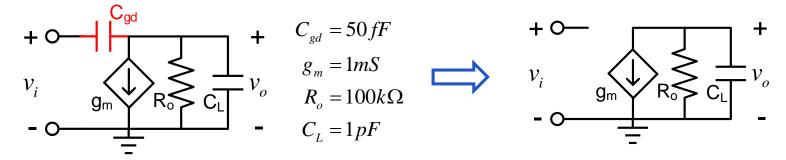

### Example

Significance calculation

| Symbol          | Operation | ε ε <sub>∞-op</sub> |           | <sup>Е</sup> 0-ор |

|-----------------|-----------|---------------------|-----------|-------------------|

| C <sub>gd</sub> | 0-ор      | 3.28e-02            | 1.41e+00  | 3.28e-02          |

| CL              | 0-ор      | 1.23e-01            | Inf / NaN | 1.23e-01          |

| R <sub>o</sub>  | 0-ор      | 3.09e+00            | Inf / NaN | 3.09e+00          |

| 9 <sub>m</sub>  | 0-ор      | 4.85e+00            | Inf / NaN | 4.85e+00          |

Process abnormal value

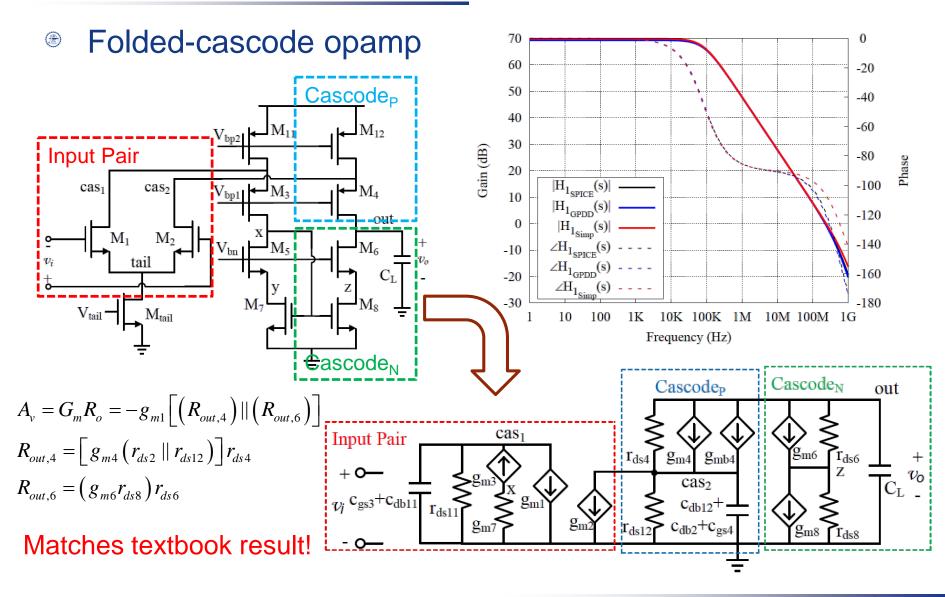

### **Test Circuit 1**

9

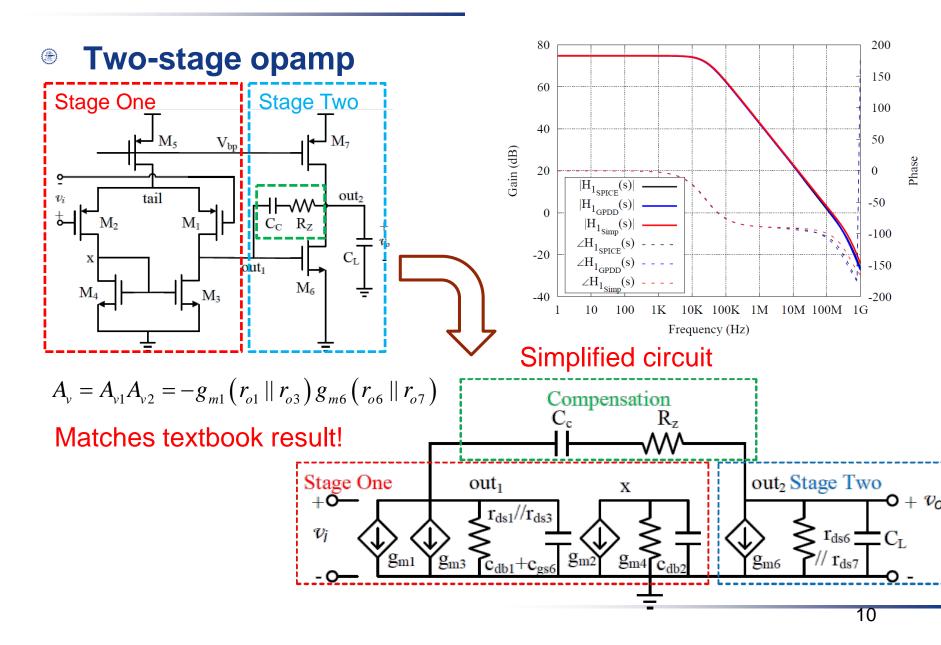

### **Test Circuit 2**

### **Poles & Zeros Results**

#### Poles & Zeros comparison for two-stage opamp

| Туре  | Original Circuit (Hz) | Low-order Model (Hz) |  |  |

|-------|-----------------------|----------------------|--|--|

| Poles | -24.6K                | -25.6KHz             |  |  |

|       | -19.4M                |                      |  |  |

|       | -374.1M±65.1M         | -375.8MHz            |  |  |

| Zeros | -21.2M                |                      |  |  |

|       | -298.0M               | -298.1M              |  |  |

#### Model order comparison

|                               | <b>Original Circuits</b> |         | Low-order Models |         |

|-------------------------------|--------------------------|---------|------------------|---------|

| Circuit Types                 | # poles                  | # zeros | # poles          | # zeros |

| Folded-Cascode                | 9                        | 8       | 3                | 1       |

| 2-stage with nulling resistor | 6                        | 6       | 4                | 2       |

| 2-stage with voltage buffer   | 6                        | 6       | 3                | 2       |

| 2-stage with current buffer   | 7                        | 7       | 4                | 2       |

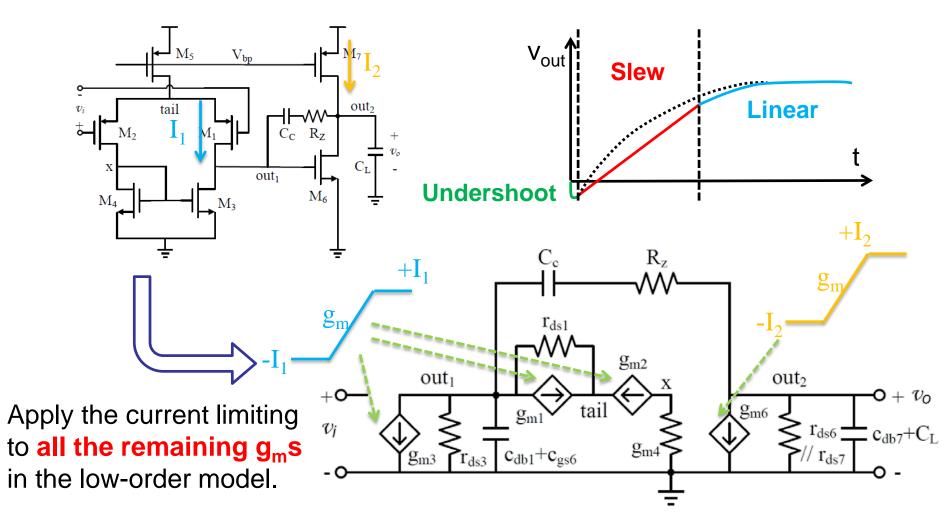

### **Time-Domain Model Review**

#### Slew-Settling Behavior

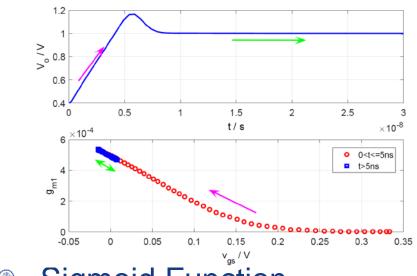

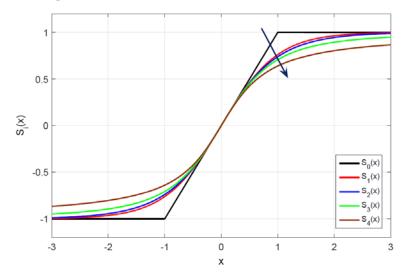

### **Nonlinear Function Selection**

Varying gm during the slew process

Sigmoid Function

For previous works on slewsettling model, g<sub>m</sub> was assumed zero during the entire slewing period. Actually, g<sub>m</sub> hikes gradually as the MOSFET gatesource voltage rises by degrees.

$$S_{0}(x) = \begin{cases} 1 & x \ge 1 \\ x & -1 \le x < 1 \\ -1 & x < 1 \end{cases}$$

$$S_{1}(x) = \tanh(x)$$

$$S_{2}(x) = \frac{2}{\pi} gd\left(\frac{\pi}{2}x\right) = \frac{2}{\pi} \arcsin\left(\tanh\left(\frac{\pi}{2}x\right)\right)$$

$$S_{3}(x) = \frac{x}{\sqrt{1+x^{2}}}$$

$$S_{4}(x) = \frac{2}{\pi} \arctan\left(\frac{\pi}{2}x\right)$$

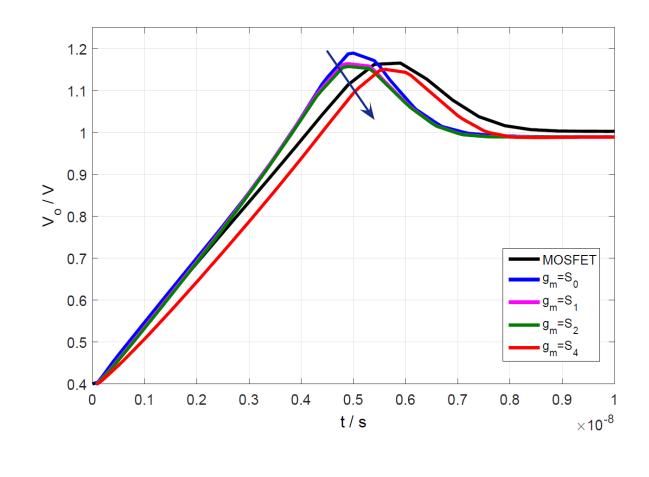

### **Experimental Results**

#### Output voltage with different sigmoid functions

The arrow exhibits the same order as shown in the previous slide.

$S_0$ ,  $S_1$ ,  $S_2$  all have better performance in slew rate estimation, however,  $S_4$  has a good agreement with transistor-level simulation in settling time prediction.

S3 is promising in both regions, but  $S_3$ can't converge in HSPICE simulation.

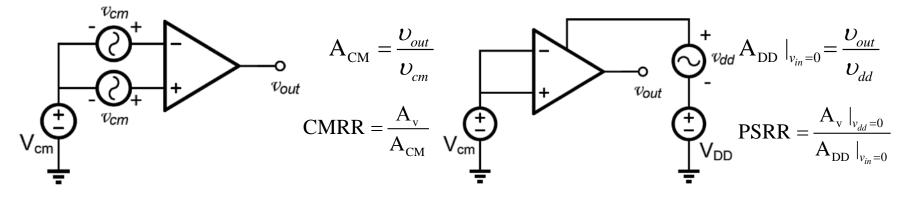

### **CMRR/PSRR** Analysis

### Introduction to CMRR & PSRR

CMRR: Common Mode Rejection Ratio PSRR: Power Supply Rejection Ratio

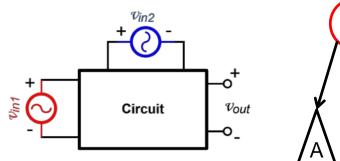

GPDD Multiport Construction

$$H_{1}(s) = \frac{f_{A}(A)}{f_{C}(C)}$$

$$H_{2}(s) = \frac{f_{B}(B)}{f_{C}(C)}$$

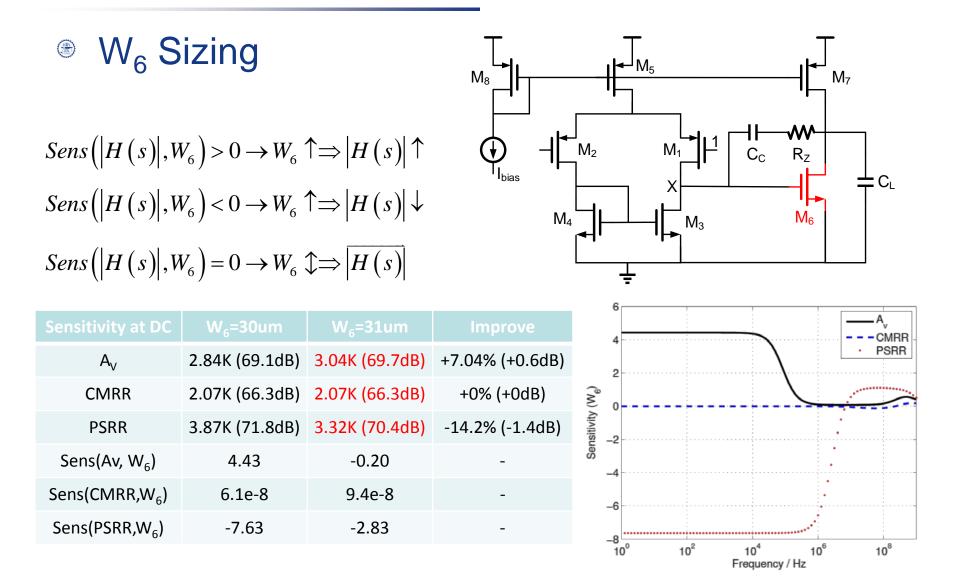

### **Multi-port Analysis for Opamp Sizing**

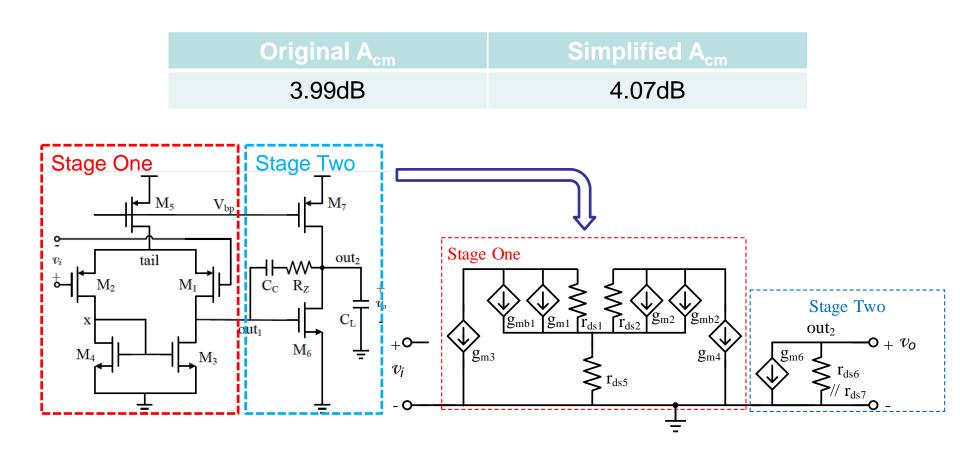

### **Model Generation for Common Mode Gain**

- Same procedure applied to common-mode gain A<sub>cm</sub>

- Significance Selection (Only consider A<sub>cm</sub> for now)

### Conclusion

- GPDD symbolic construction can be applied to topological circuit reduction.

- Can <u>automatically generate</u> small-signal model as **behavioral model** for system-level use.

- Extended to generate large-signal model for slew-settling analysis

- Explored the possibility for multi-port model generation on GPDD.

Thanks! Q & A