# Topological Symbolic Simplification for Analog Design

Hanbin Hu, Guoyong Shi (presenter),

Dept. of Micro/Nano-electronics, Shanghai Jiao Tong University, Shanghai, China Andy Tai and Frank Lee Synopsys, Inc.

ISCAS 2015, Lisbon, Portugal, May 25-27, 2015

# Outline

- Research motivation

- Background review

- Contribution

- Application of symbolic topology representation to topology simplification

- Strategy for ordering symbol significance

- Demonstration of the effectiveness of symbolic reduction

- Experimental results

- Conclusion

# **Motivation for Topology Simplification**

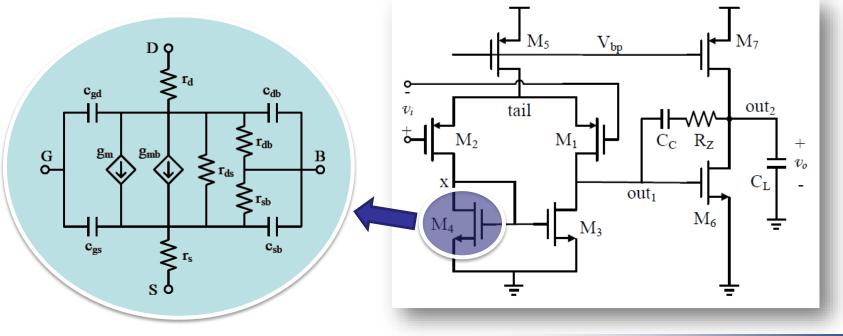

- Lumped small-signal model is popular in analog circuit design.

- Direct symbolic analysis generates non-interpretable results.

- Simplification helps deriving circuit insight and visualizing dominant circuit components

# **Symbolic Analysis for Simplification**

Symbolic analysis can generate the symbolic circuit transfer functions

- Reusable

- **but suffers** from **exponentially growing complexity** (in circuits size)

- Symbolic simplifications are commonly used: SBG, SDG, SAG.

- Simplification "Before / During / After" Generation

- Previous research in this area emphasizes simplifying symbolic expressions, rather than topology

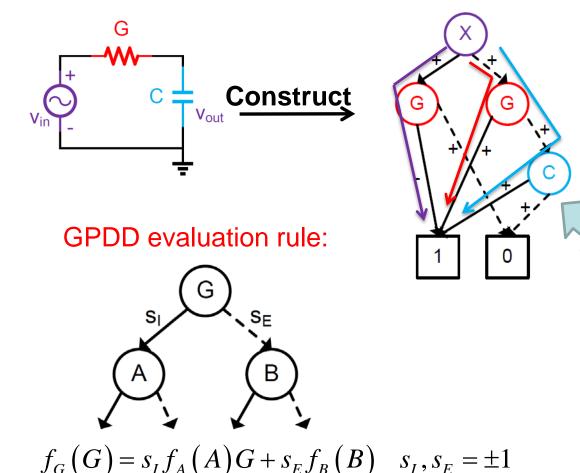

# A Symbolic Method capable of Handling Topology

- Graph-Paired Decision Diagram (GPDD) A BDD

- A topology-based analysis method

This diagram actually encodes the circuit topology

Paths in the GPDD are symbolic terms

$$-XG + G + sC = 0$$

$$\Rightarrow H(s) = \frac{1}{X} = \frac{G}{G + sC}$$

G. Shi (TCAD, 2013)

#### **Feature of Symbols in GPDD**

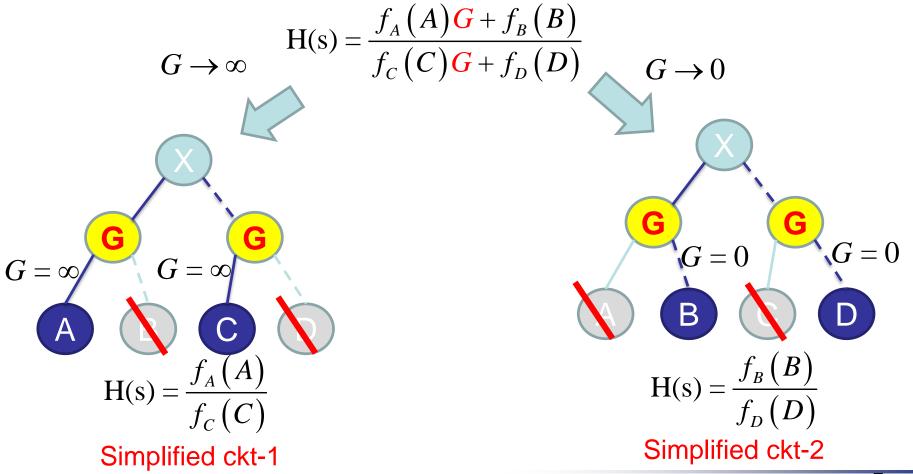

$$H(s) = \frac{f_A(A)G + f_B(B)}{f_C(C)G + f_D(D)}$$

The numerator and denominator are **affine functions** of an arbitrary symbol; "G" in this example.

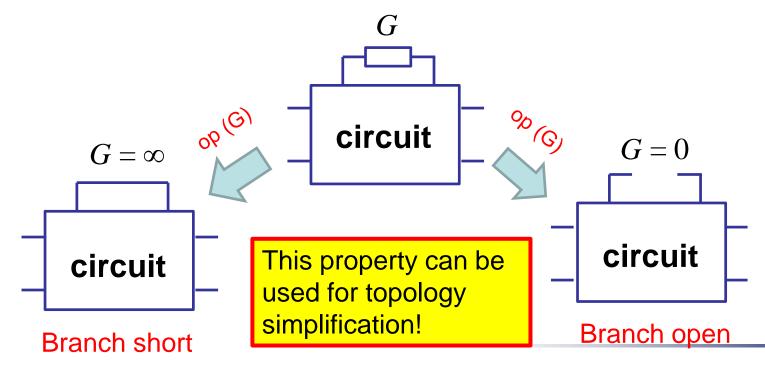

"G" taking 0 or  $\infty$  results in two different reduced circuits:

## **Taking Element Limits in GPDD**

Setting a symbol to 0 or ∞ can be manipulated directly in GPDD! -- (just tracing along different paths)

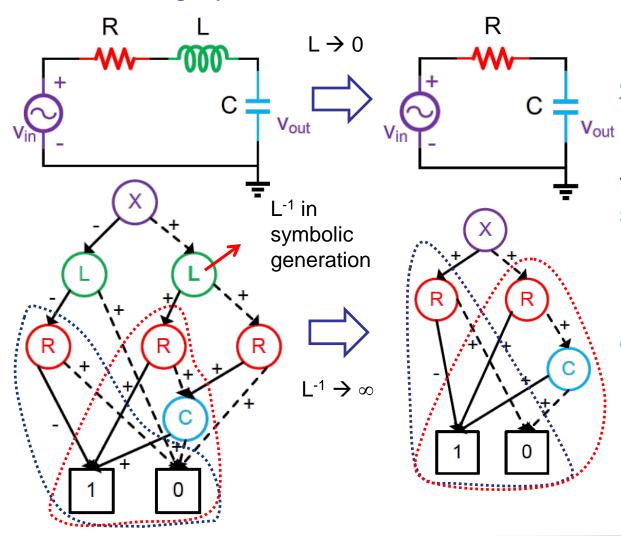

## Example

Reducing symbol L from an RLC circuit

Comments:

Obtaining GPDD for the reduced ckt is straightforward.

GPDD is a good media for topological circuit reduction.

### **Main Contributions of this Work**

- Proposal of GPDD based reduction scheme

- Done!

- An assessing method for assigning significance to each circuit element

- "significance" to be defined later

- Sorting element by their significance

- Removing those least significant elements

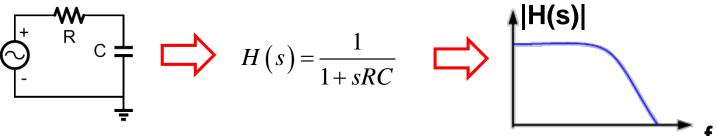

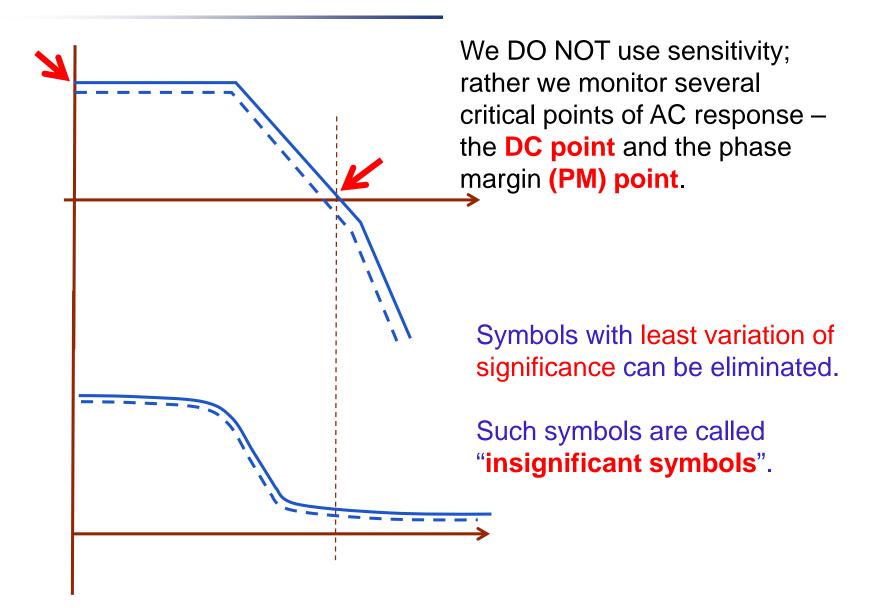

#### **Feature of Frequency Response**

## **Significance Assessment**

- Definition of Symbol Significance :

- The total (relative) variation of two monitored quantities when a selected element (say, G) is operated with 0-operation or  $\infty$ -operation.  $G = \infty$

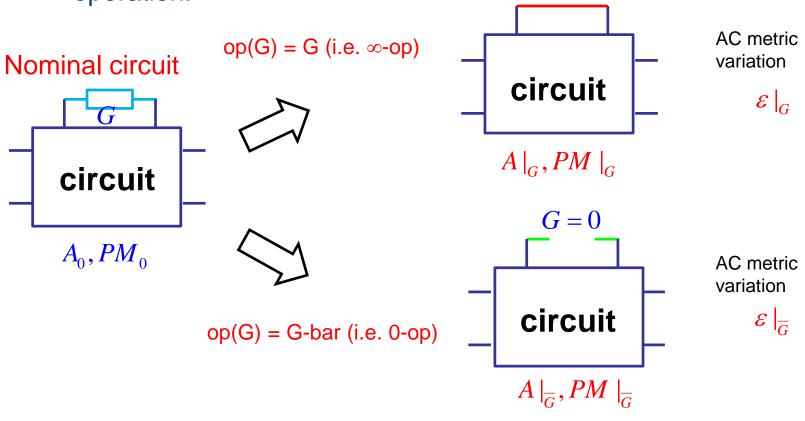

#### **Symbol Operation & Metric Variation**

$$\varepsilon \mid_{G} = \sqrt{\left(\frac{A\mid_{G} - A_{0}}{A_{0}}\right)^{2} + \left(\frac{PM\mid_{G} - PM_{0}}{PM_{0}}\right)^{2}} \quad \text{op}(G) = G \text{ (short } G)$$

$$\varepsilon \mid_{\overline{G}} = \sqrt{\left(\frac{A\mid_{\overline{G}} - A_{0}}{A_{0}}\right)^{2} + \left(\frac{PM\mid_{\overline{G}} - PM_{0}}{PM_{0}}\right)^{2}} \quad \text{op}(G) = G\text{-bar (open } G)$$

Significance:

$$E_{op(G)} = \min \left\{ \varepsilon |_{G}, \varepsilon |_{\overline{G}} \right\}$$

op(G) = G or G-bar

Choose the operation with smaller metric variation

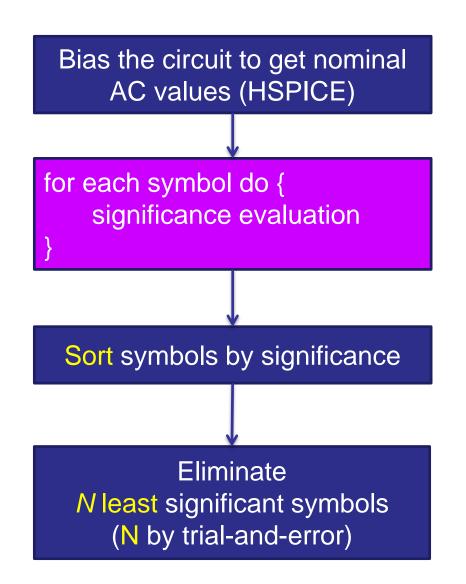

### **Simplification Flow**

#### **Comments on the Flow**

- The symbolic GPDD is constructed only once for each circuit,

- and repeatedly used in significance evaluation for all symbols.

- The complexity for the significance evaluation of all symbols is proportional to the size of GPDD x num of symbols in the circuit.

- Several seconds in our experiment

# **Experimental Results**

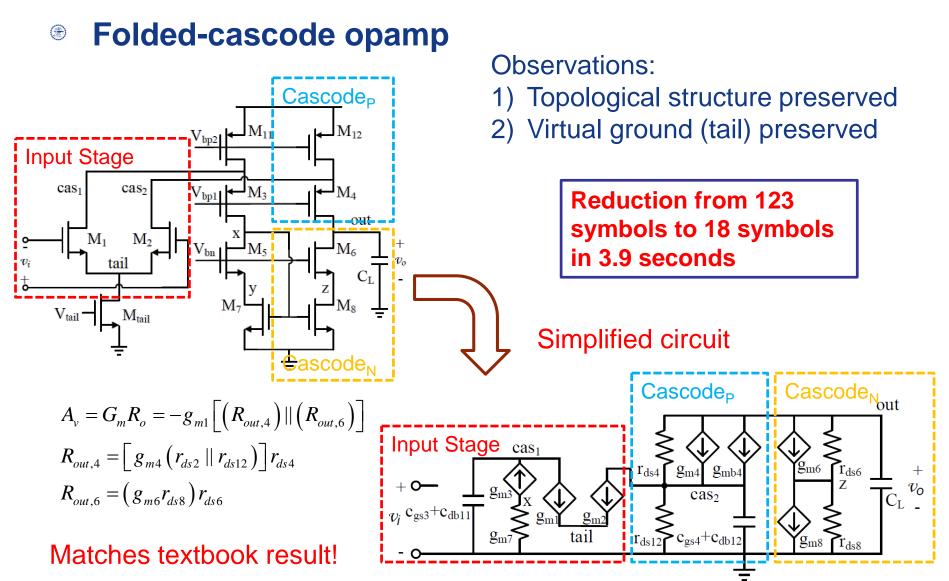

## **Test Circuit 1**

#### Test Circuit 1 (cont'd)

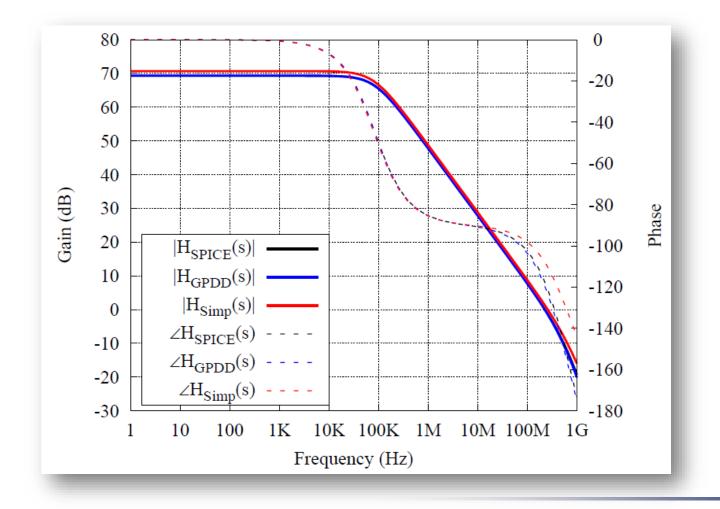

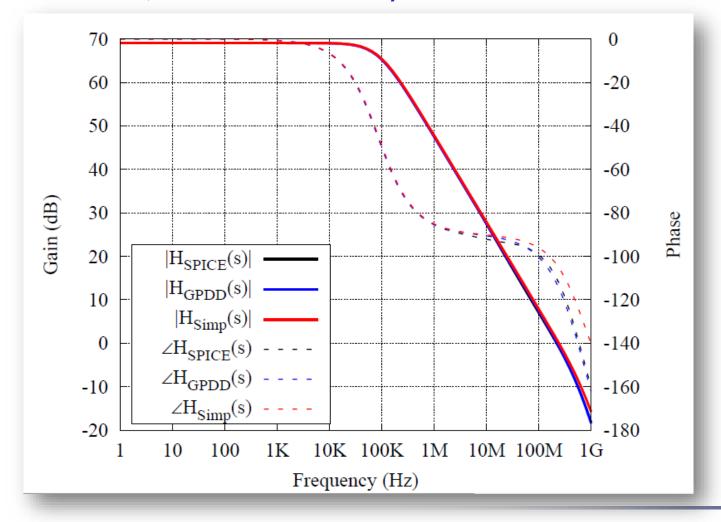

# Check the frequency response (comparing full ckt, reduced ckt, and SPICE results)

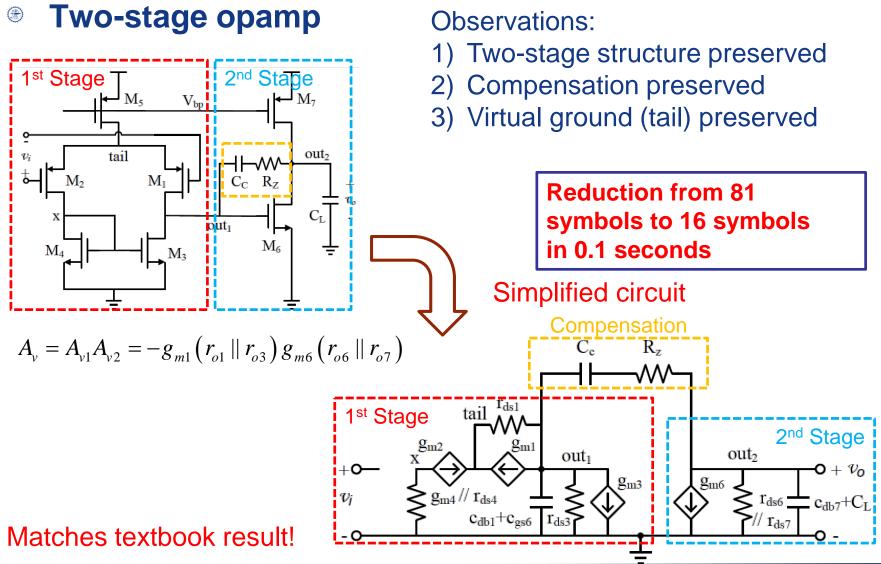

## **Test Circuit 2**

#### Test Circuit 2 (cont'd)

# Check the frequency response (comparing full ckt, reduced ckt, and SPICE results)

### **Further Study**

- Improving the assessment metrics

- Incorporating other design metrics (CMRR and PSRR, ...)

- Robustness of generated models

- Extensible to slew-settling model

- Help extraction of symbolic dominant poles/zeros

- Graphical interface support for readable schematic

- Automatically determine the num of symbols to eliminate

### Conclusion

- GPDD symbolic construction can be applied to topological circuit reduction.

- Can <u>automatically generate</u> small-signal model as behavioral model for system-level use.

- Can be extended to generate large-signal model for slew-settling analysis

- Future work

Thanks! Q & A